Product Summary

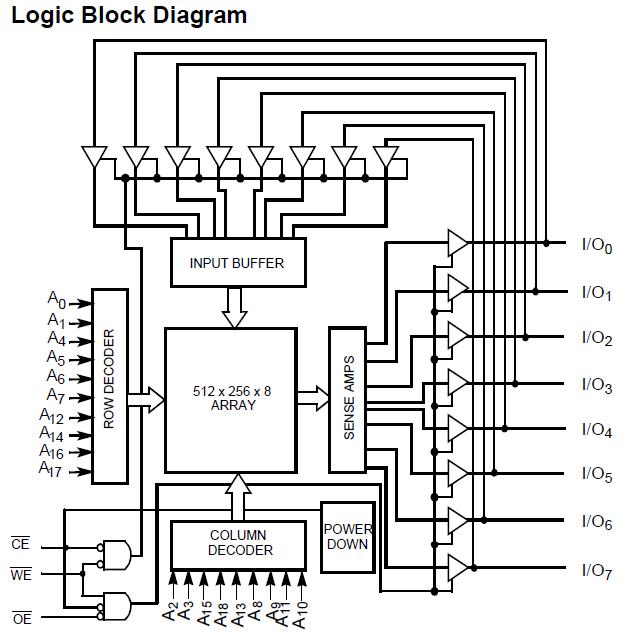

The CY62148BLL-70SXI is a high-performance CMOS static RAM, which is organized as 512K words by 8 bits. Easy memory expansion is provided by an active LOW Chip Enable (CE), an active LOW Output Enable (OE), and three-state drivers. The CY62148BLL-70SXI has an automatic power-down feature that reduces power consumption by more than 99% when deselected.

Parametrics

CY62148BLL-70SXI absolute maximum ratings: (1)Storage Temperature: –65℃ to +150℃; (2)Ambient Temperature with Power Applied: –55℃ to +125℃; (3)Supply Voltage to Ground Potential (Pin 28 to Pin 14): –0.5V to +7.0V; (4)DC Voltage Applied to Outputs in High-Z State: –0.5V to VCC + 0.5V; (5)DC Input Voltage: –0.5V to VCC + 0.5V; (6)Output Current into Outputs (LOW): 20 mA; (7)Static Discharge Voltage > 2001V; (8)Latch-up Current > 200 mA.

Features

CY62148BLL-70SXI features: (1)4.5V-5.5V operation; (2)Low active power: typical active current: 2.5 mA @ f = 1 MHz, typical active current: 12.5 mA @ f = fmax; (3)Low standby current; (4)Automatic power-down when deselected; (5)TTL-compatible inputs and outputs; (6)Easy memory expansion with CE and OE features; (7)CMOS for optimum speed/power.

Diagrams

|

CY62126BV |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30L-55BVXE |

Cypress Semiconductor |

SRAM SLO 3.0V SUPER LO PWR 64K X 16 SRAM |

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30L-55BVXET |

Cypress Semiconductor |

SRAM SLO 3.0V SUPER LO PWR 64K X 16 SRAM |

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30L-55ZSXE |

Cypress Semiconductor |

SRAM SLO 3.0V SUPER LO PWR 64K X 16 SRAM |

Data Sheet |

Negotiable |

|

||||

|

CY62126DV30L-55ZSXET |

Cypress Semiconductor |

SRAM SLO 3.0V SUPER LO PWR 64K X 16 SRAM |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))